O Compute Express Link (CXL) acaba de dar um salto significativo com o anúncio oficial da versão 4.0, que praticamente dobra a largura de banda efetiva e estabelece o padrão PCIe 7.0 como base obrigatória para toda a especificação. Essa mudança não é apenas técnica - ela redefine completamente o planejamento de hardware para data centers e acelera a corrida por plataformas capazes de lidar com cargas massivas de IA e computação heterogênea em escala industrial.

O papel fundamental do CXL na computação moderna

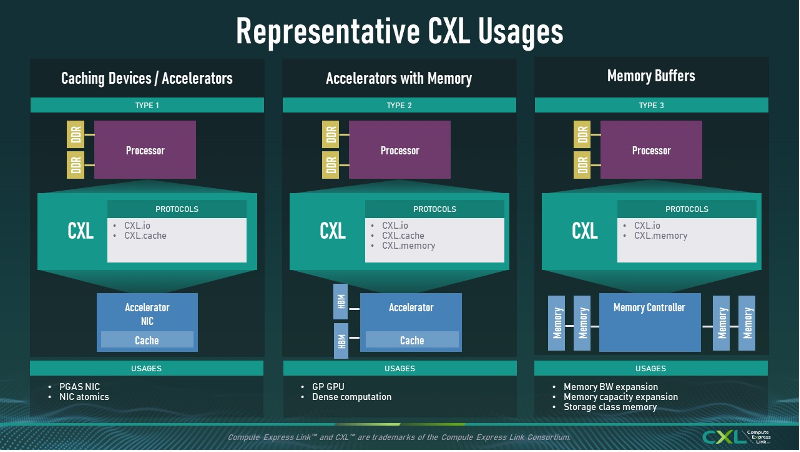

Na minha experiência acompanhando evoluções de hardware, poucas tecnologias surgiram com um propósito tão claro quanto o CXL. Ele foi criado para resolver um problema que se tornou cada vez mais evidente: a dificuldade de diferentes componentes trocarem dados rapidamente e de forma coerente, sem duplicação desnecessária de memória e sem depender exclusivamente da CPU como intermediária.

E olha que o cenário atual é complexo - servidores modernos combinam CPUs, GPUs, aceleradores de IA, DPUs, FPGAs e múltiplas camadas de memória em formatos variados. O fluxo de dados precisa ser muito mais eficiente do que o fornecido pelas interconexões tradicionais. É aí que o CXL entra como uma ponte de alta velocidade com coerência de memória, permitindo que vários dispositivos acessem e compartilhem o mesmo espaço de memória sem cópias redundantes.

O que mais me impressiona é como essa tecnologia se tornou crucial justamente agora. Com o crescimento explosivo da IA generativa, modelos cada vez maiores exigem quantidades absurdas de memória acessível. A estratégia tradicional de empilhar módulos de DRAM no mesmo soquete está literalmente chegando ao limite físico e térmico. O CXL surge como alternativa escalável, permitindo construir servidores com memória desagregada compartilhada entre racks, topologias flexíveis usando switches e, claro, mais largura de banda por enlace.

As principais inovações do CXL 4.0

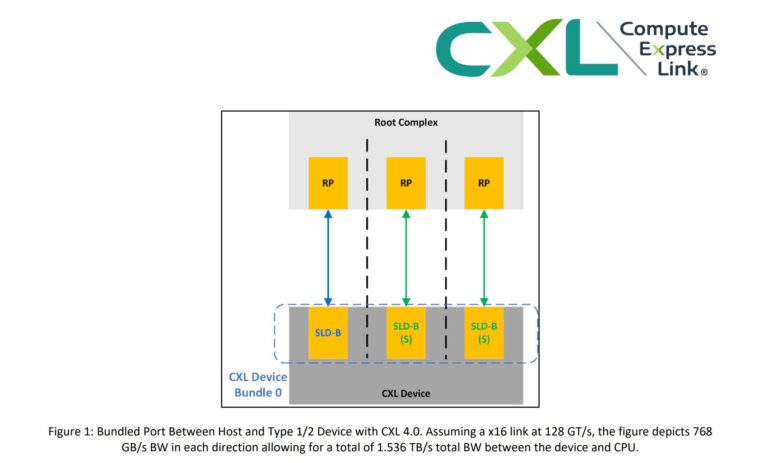

O CXL Consortium publicou formalmente a especificação 4.0, que salta de 64 GT/s para impressionantes 128 GT/s, apoiando-se diretamente na interface PCIe 7.0 como camada física. Esse é o maior avanço desde a criação do padrão e consolida o CXL como eixo central de arquiteturas que combinam múltiplos tipos de processadores e memória.

Segundo o documento oficial, a evolução mantém o formato de flit de 256 Bytes, acrescenta modo nativo x2, viabiliza até quatro retimers por canal e entrega melhorias relevantes de RAS, como visibilidade mais ampla de erros e mecanismos avançados de manutenção.

"A liberação do CXL 4.0 faz parte de um novo estágio na conexão coerente de memória, ampliando a largura de banda e preservando compatibilidade com gerações anteriores, ao mesmo tempo em que prepara o setor para novos modelos de uso"

Derek Rohde, presidente do consórcio

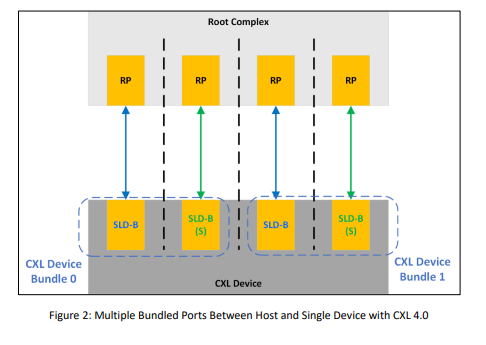

Um dos recursos que mais chama atenção é o Bundled Port, que permite combinar dois enlaces físicos para ampliar a banda efetiva entre host e dispositivos. Isso facilita o uso de aceleradores de IA, DPUs e placas híbridas que precisam transmitir grandes volumes de dados com latência controlada. A funcionalidade sinaliza uma aproximação maior entre o CXL e arquiteturas de interconexão que trabalham com agregação de links.

Impacto prático e adoção no mercado

A migração do CXL para PCIe 7.0 não é apenas simbólica - ela confirma que todo o ecossistema de servidores, placas-mãe, aceleradores e controladores terá que avançar para uma plataforma completamente alinhada ao novo barramento. O padrão se torna, portanto, pré-requisito para qualquer implementação real de CXL 4.0.

E isso impacta diretamente fornecedores de hardware que ainda estão estabilizando produtos com PCIe 5.0 e planejando a chegada do PCIe 6.0. A janela de adoção pode se acelerar dramaticamente, especialmente em segmentos como IA generativa, HPC e bancos de memória desagregada.

O que me surpreende é como, apesar de todas essas mudanças radicais, o consórcio manteve compatibilidade total com CXL 1.x, 2.0 e 3.x. Essa estratégia é fundamental para fabricantes que dependem de ciclos longos de desenvolvimento e preserva investimentos de gerações anteriores. Facilita combinações de dispositivos, retimers e switches em data centers híbridos, típicos de grandes provedores de nuvem.

Com a multiplicação de workloads de IA e a necessidade de transportar grandes volumes de dados entre chips heterogêneos, o CXL 4.0 chega como peça estratégica na construção de servidores escaláveis. A dependência de PCIe 7.0 também funciona como um acelerador da próxima geração de plataformas, empurrando OEMs e fabricantes de processadores para ciclos de atualização mais rápidos.

O lançamento da especificação 4.0 não fecha um ciclo, mas abre uma corrida por soluções capazes de absorver essa largura de banda e explorar a nova lógica de fabric coerente. Assim que PCIe 7.0 ganhar tração, o CXL tende a se tornar o elo mais visível entre CPU, aceleradores de IA e camadas de memória cada vez mais distribuídas.

Fonte: Compute Express Link

Desafios de implementação e o ecossistema em evolução

A transição para CXL 4.0 não será simples, e isso é algo que precisa ser dito com clareza. A exigência do PCIe 7.0 como base traz desafios de sinalização que vão muito além do que a indústria enfrentou com versões anteriores. A frequência mais alta significa atenuação de sinal mais severa, exigindo materiais de PCB mais avançados e técnicas de equalização sofisticadas.

Na prática, isso se traduz em custos mais elevados para placas-mãe de servidores e possivelmente uma adoção inicial concentrada em aplicações de alto desempenho onde o ROI justifica o investimento. Fabricantes terão que lidar com desafios de integridade de sinal que podem limitar o comprimento físico dos traços, impactando diretamente o design de racks e a distribuição de componentes dentro do data center.

O que me impressiona é como o consórcio parece estar antecipando esses desafios. A especificação inclui melhorias significativas nos mecanismos de treinamento de link e equalização adaptativa, que são cruciais para manter a estabilidade em altas velocidades. Mas ainda assim, a migração de PCIe 5.0/6.0 para 7.0 representa um salto técnico considerável que exigirá tempo e investimento massivo em P&D.

O papel dos switches CXL na arquitetura de data centers

Uma das áreas onde o CXL 4.0 pode realmente brilhar é na topologia com switches. Com a largura de banda dobrada, os switches CXL se tornam ainda mais capazes de gerenciar pools de memória desagregada e conectar múltiplos hosts a aceleradores compartilhados. Isso permite arquiteturas verdadeiramente flexíveis onde recursos podem ser alocados dinamicamente conforme a demanda.

Imagine um cenário onde um cluster de servidores pode acessar um pool massivo de memória CXL durante picos de processamento de IA, e depois liberar esses recursos quando a carga diminui. Essa eficiência operacional é exatamente o que grandes provedores de nuvem buscam, e o CXL 4.0 entrega a base técnica para tornar isso realidade em escala.

Os switches CXL 4.0 também facilitam a criação de hierarquias de memória mais complexas, combinando DRAM local com memória CXL-attached e até mesmo storage classe memory. Essa abordagem híbrida permite otimizar custos e desempenho de forma muito mais granular do que era possível anteriormente. E com a latência reduzida em comparação com versões anteriores, a penalidade de performance ao acessar memória remota se torna cada vez menos significativa.

A corrida pela memória CXL e os novos players do mercado

O anúncio do CXL 4.0 está acelerando investimentos em um segmento que até recentemente era dominado por poucos players. Fabricantes de memória como Samsung, SK Hynix e Micron estão desenvolvendo módulos CXL específicos, enquanto empresas como Astera Labs, Rambus e Synopsys focam em controladores e IP.

O que é particularmente interessante é como startups estão encontrando espaço nesse ecossistema. Empresas que focam em otimização de software para memória desagregada ou em soluções de gerenciamento para pools CXL estão surgindo, indicando que o mercado reconhece a complexidade envolvida em extrair o máximo dessas novas arquiteturas.

"A memória CXL não é apenas sobre capacidade - é sobre inteligência na forma como gerenciamos hierarquias complexas e otimizamos o acesso para diferentes cargas de trabalho"

Analista de data centers, empresa de pesquisa de mercado

Do ponto de vista do hardware, estamos vendo o surgimento de dispositivos CXL Type 3 (memória expandida) que vão desde módulos simples até sistemas complexos com múltiplas camadas de cache e lógica de gerenciamento integrada. Essa diversificação é saudável para o ecossistema, mas também introduz desafios de interoperabilidade que precisarão ser resolvidos através de testes rigorosos e certificações.

Implicações para desenvolvedores e administradores de sistema

Para quem está no lado do software, a chegada do CXL 4.0 traz tanto oportunidades quanto complexidades. A capacidade de endereçar pools massivos de memória compartilhada entre múltiplos dispositivos exige mudanças significativas em como aplicações são desenvolvidas e como sistemas são gerenciados.

Frameworks de programação terão que evoluir para lidar com hierarquias de memória não uniforme (NUMA) em escala muito maior do que estamos acostumados. E administradores de data center precisarão de novas ferramentas para monitorar e otimizar a utilização de memória em arquiteturas desagregadas.

O lado positivo é que muitas dessas mudanças estão sendo antecipadas. Projetos open source como Linux Kernel e hypervisors já estão incorporando suporte para CXL, e comunidades de desenvolvedores estão experimentando com novas abstrações de programação. Mas a transição não será instantânea - levará anos até que as melhores práticas para aproveitar ao máximo o CXL 4.0 sejam estabelecidas e amplamente adotadas.

O que me fascina é como essa evolução técnica está forçando uma convergência entre disciplinas que tradicionalmente operavam de forma isolada. Desenvolvedores de aplicações, engenheiros de sistemas e arquitetos de hardware precisam colaborar mais intimamente do que nunca para extrair o máximo valor dessas novas capacidades. E essa colaborção cruzada pode, por si só, levar a inovações que vão muito além do que os criadores do CXL originalmente imaginaram.

Com informações do: Adrenaline