Por mais de uma década, transistores 2D baseados em materiais bidimensionais pareciam uma promessa confinada aos laboratórios de pesquisa. Demonstrações acadêmicas eram fascinantes, mas sempre esbarravam em um obstáculo prático gigantesco: a incompatibilidade com a fabricação em massa de semicondutores. Agora, essa barreira pode estar começando a ruir. Em uma colaboração com o instituto de pesquisa imec, a Intel Foundry anunciou um avanço crucial: a integração de módulos de processo críticos para transistores 2D (2DFETs) em wafers de 300 mm, o padrão da indústria. É um passo que tira a tecnologia do reino da teoria e a coloca no caminho da realidade fabril.

O fim da linha para o silício?

A corrida pela miniaturização, que nos trouxe chips cada vez mais poderosos e eficientes, está encontrando um muro físico. Tecnologias de ponta como a Intel 18A, a Samsung SF3E e a TSMC N2 já utilizam estruturas gate-all-around (GAA), e o próximo passo previsto são os CFETs (Complementary Field-Effect Transistors), que empilham transistores verticalmente. Mas e depois? A indústria sabe que, em algum momento, o próprio silício – o material que construiu a era digital – atingirá seus limites fundamentais.

Quando os canais de silício ficarem excessivamente finos, o controle eletrostático sobre a corrente se degrada e a mobilidade dos elétrons cai. É como tentar escoar um rio por um canudo cada vez mais fino e irregular – a eficiência despenca. É aqui que os materiais 2D entram em cena como uma solução potencialmente revolucionária. Imagine um canal com a espessura de apenas um ou poucos átomos. Essa finura extrema permite um controle excepcional sobre a passagem de corrente, algo que o silício em escalas atômicas simplesmente não consegue oferecer com a mesma robustez.

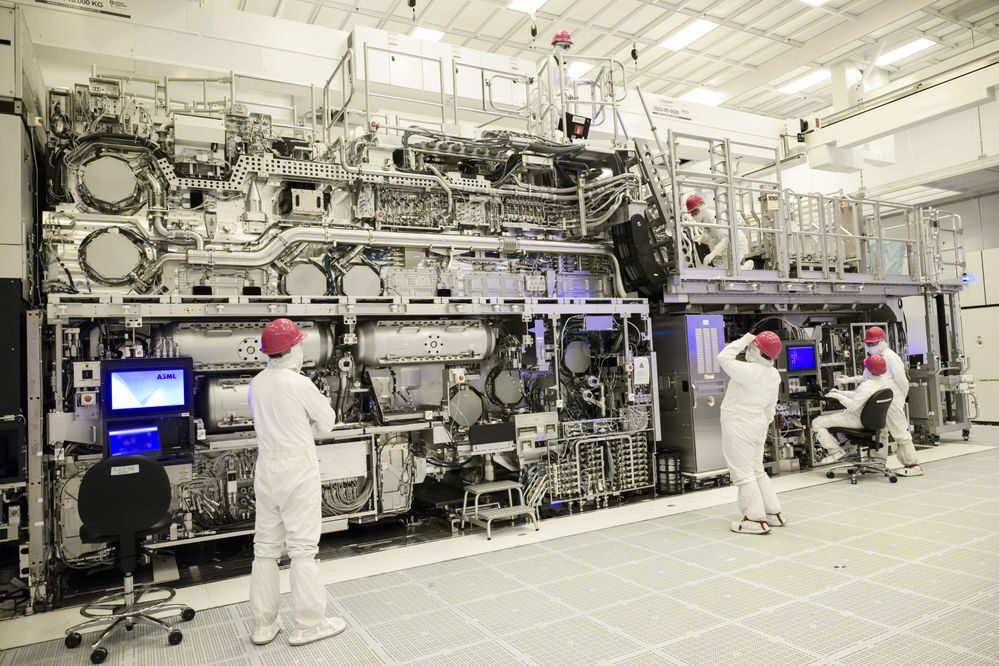

A ponte entre o laboratório e a fábrica

O grande desafio nunca foi provar que os transistores 2D funcionam em condições controladas. O problema real, aquele que mantinha a tecnologia no limbo, era a fabricação. Como integrar materiais extremamente delicados, como os dicalcogenetos de metais de transição (TMDs) – WS₂ e MoS₂ para transistores tipo 'n', WSe₂ para tipo 'p' – em uma linha de produção que manipula wafers de 300 mm com processos altamente padronizados e, por vezes, agressivos?

A inovação apresentada pela Intel e pelo imec é engenhosa. Eles desenvolveram um esquema de integração de contatos e porta que protege esses materiais frágeis. Primeiro, cultivam camadas 2D de alta qualidade e as revestem com uma pilha protetora de óxidos. Em seguida, usam uma técnica de gravação seletiva extremamente controlada para formar os contatos elétricos no estilo "damasceno", um método já consagrado na indústria. Essa abordagem é fundamental porque preserva a integridade do canal 2D subjacente, que é sensível como uma bolha de sabão à contaminação e a danos físicos.

Resolver o problema dos contatos de baixa resistência e escaláveis era um dos maiores entraves. Se você tem um material maravilhoso para conduzir corrente, mas não consegue conectá-lo ao resto do circuito de forma eficiente e reproduzível, a tecnologia é inútil. Ao demonstrar módulos de porta fabricáveis, eles derrubaram outro obstáculo histórico. Na minha opinião, esse é o tipo de avanço "chato" mas absolutamente vital – é a engenharia de processo pesada que transforma uma curiosidade científica em uma opção de fabricação.

Um investimento no futuro distante

Aqui é importante ajustar as expectativas. Não espere comprar um laptop com CPU 2D na próxima Black Friday, ou mesmo na próxima década. A Intel e o imec são bastante claros: os transistores 2D baseados nesses materiais são uma tecnologia para um futuro mais distante, possivelmente na segunda metade dos anos 2030 ou mesmo na década de 2040.

Então, qual o sentido de anunciar isso agora? A estratégia é sobre redução de risco e aceleração do desenvolvimento. Ao validar esses módulos críticos em um ambiente que simula uma fábrica real, a Intel Foundry está criando um "kit de ferramentas" para o futuro. Isso permite que seus clientes e suas próprias equipes de projeto comecem a avaliar e modelar circuitos usando canais 2D com premissas realistas, muito antes de a tecnologia estar pronta para produção.

Pense nisso como planejar uma viagem interplanetária. Você não espera o combustível de antimatéria ficar pronto para começar a desenhar a nave. Você desenvolve os sistemas de suporte de vida, a estrutura e a eletrônica com base no que sabe que será necessário, resolvendo problemas antecipadamente. A Intel está tratando os materiais 2D como uma opção futura crítica, desenvolvendo os processos em paralelo com parceiros como o imec. A ideia é enfrentar os desafios de fabricação de cara, evitando surpresas desagradáveis – e caras – na reta final, quando a substituição do silício se tornar uma necessidade urgente.

Para a Intel Foundry, esse anúncio também é uma declaração de capacidade. É um sinal para o mercado, para os investidores e para os clientes de que a empresa não está apenas focada no próximo nó de processo, mas está engajada em pesquisas de longo prazo que definirão a computação das próximas décadas. Em um setor onde a liderança tecnológica é tudo, demonstrar que você está pensando em 2040 enquanto seus concorrentes falam de 2027 é uma jogada estratégica poderosa. O trabalho árduo e meticuloso de hoje está pavimentando a estrada para as revoluções de amanhã.

Os desafios que ainda separam a promessa da produção

Mas vamos ser realistas: superar a barreira dos 300 mm é um marco monumental, mas não é a linha de chegada. É mais como ter finalmente construído uma ponte sobre um grande abismo. Agora, o trabalho de pavimentar a estrada e garantir que ela suporte o tráfego pesado começa de verdade. E que tipo de "tráfego" estamos falando? A indústria exige não apenas funcionalidade, mas uniformidade, rendimento e confiabilidade em escala colossal.

Um dos maiores obstáculos à frente é a deposição uniforme desses materiais 2D em wafers inteiros. Cultivar uma camada perfeita de MoS₂ em um pequeno chip de laboratório é uma coisa. Fazer isso centenas de vezes, com precisão atômica, em um disco de silício de 300 mm de diâmetro, é um desafio de física e engenharia de outro patamar. Qualquer variação na espessura, na cristalinidade ou na pureza do material pode resultar em transistores com desempenho inconsistente – um pesadelo para qualquer fabricante que precisa garantir que cada chip dentro de um lote funcione exatamente como projetado.

E não podemos esquecer da integração com o resto do processo. Um transistor não vive sozinho. Ele precisa se conectar a interconexões de metal, a dielétricos, a outros transistores. Como esses materiais 2D, com suas propriedades superficiais únicas, vão interagir com as dezenas de outras camadas de materiais que compõem um chip moderno? A compatibilidade térmica é outra grande questão. Os processos de fabricação envolvem ciclos de aquecimento intenso. Esses materiais atômicos podem sobreviver a isso sem se degradar ou contaminar o wafer?

Na minha visão, é aqui que a colaboração com um instituto como o imec se mostra tão valiosa. Eles funcionam como um campo de testes de "pré-produção", um ambiente onde esses problemas de integração de sistema podem ser atacados anos antes de uma fábrica comercial sequer considerar a tecnologia. Eles podem simular, testar e falhar em um ritmo que uma linha de produção de US$ 20 bilhões simplesmente não pode se permitir.

Além do silício: um ecossistema de materiais em ascensão

Falar em "transistores 2D" muitas vezes soa como uma coisa só, mas a realidade é muito mais rica – e complicada. O trabalho da Intel e do imec foca em TMDs como WS₂ e MoS₂, que são candidatos fortes. Mas eles são apenas alguns soldados em um exército crescente de materiais bidimensionais sendo investigados em laboratórios ao redor do mundo.

O grafeno foi a estrela inicial, famoso por sua condutividade excepcional. No entanto, ele tem um grande defeito para transistores lógicos: falta de um *bandgap* natural, uma propriedade essencial para ligar e desligar a corrente de forma nítida. É um material fantástico para interconexões, mas não tanto para o canal do transistor em si. Já os TMDs, como os usados no estudo, possuem esse *bandgap* natural, o que os torna mais adequados.

Mas a busca não para. Pesquisadores exploram outros materiais, como o fosforeno (fósforo negro) ou heteroestruturas que empilham diferentes materiais 2D para criar propriedades sob medida. Imagine poder "projetar" um material camada por camada atômica, como um sanduíche quântico, para otimizar a condução de elétrons, o controle da porta e a dissipação de calor. É um nível de personalização que o silício, por mais que o dopemos e moldemos, nunca poderá oferecer.

O que isso significa na prática? Que a decisão final sobre qual material 2D vencerá não é técnica pura. É uma equação complexa que envolve desempenho, *manufacturability*, custo e propriedades de integração. A Intel, ao desenvolver processos modulares, está essencialmente criando uma plataforma. A ideia pode ser: "Aqui está como integramos um canal 2D genérico". Se amanhã surgir um material melhor que o MoS₂, a infraestrutura de processo básica – os métodos de deposição, gravação e contato – já estará parcialmente desenvolvida, acelerando sua adoção.

O impacto silencioso no design de chips

Enquanto os engenheiros de processo lutam com átomos e wafers, há outra revolução acontecendo em paralelo, nos domínios do software de design. E esse é um ponto que muitas análises ignoram. Desenhar um circuito para rodar em silício é uma coisa. Desenhar um circuito para explorar as propriedades únicas de um canal 2D é completamente diferente.

As ferramentas de EDA (Electronic Design Automation) que os engenheiros usam para projetar chips são baseadas em modelos físicos profundamente enraizados no comportamento do silício. Como os elétrons se movem, como o calor se dissipa, como a tensão se distribui – tudo isso é modelado com décadas de dados empíricos do silício. Colocar um material radicalmente novo no coração do transistor exige que todos esses modelos sejam reescritos ou, pelo menos, drasticamente recalibrados.

É por isso que o anúncio de "módulos fabricáveis" é tão crucial também para os designers. Agora, eles podem começar a obter dados do mundo real sobre como esses transistores 2D se comportam em estruturas integradas. Esses dados alimentarão novos modelos de simulação. E aí a magia acontece: os arquitetos de chip podem começar a explorar, em software, arquiteturas radicalmente novas que seriam ineficientes ou impossíveis com o silício.

Talvez os canais 2D, com seu controle eletrostático superior, permitam operar com voltagens muito mais baixas, abrindo caminho para chips que são ordens de grandeza mais eficientes em energia. Ou talvez sua finura extrema permita novas topologias de empacotamento 3D, empilhando lógica e memória de formas hoje inimagináveis. A disponibilidade antecipada desses modelos de processo é o que permitirá que essa criatividade arquitetônica floresça, garantindo que, quando os transistores 2D chegarem à linha de produção, já existam designs revolucionários prontos para serem fabricados. O hardware do futuro está sendo desenhado hoje, em telas de computador, graças a esses avanços meticulosos no chão de fábrica.

Com informações do: Adrenaline